### 7E4048

# B. Tech. VII Semester (Main/Back) Examination 2013

# ELECTRONICS & COMMUNICATION # DECO

Time: 3 Hours

Min. Passing Marks: 24 Maximum Marks: 80

### Instruction to Candidates:

Attempt any five questions, selecting one question from each unit. All questions carry equal marks. (Schematic diagrams must be shown wherever necessary. Any data you feel missing suitably be assumed and stated clearly. Units of quantities used/calculated must be stated clearly.)

## ⟨Unit-T'⟩

- (a) What are the types of MOSFETs. Draw the schematic diagrams and circuit symbols for all. [4]

- (b) Explain the operation of enhancement NMOS using suitable diagrams. Also draw the characteristics and justify that it is a voltage controlled current device after seeing the characteristics. [3]

#### OR

- (a) Explain the NMOS fabrication process with the help of neat diagrams.

- Write the steps to fabricate n-well CMOS (NOT the diagrams).

- (c) Write a short note on "depletion mode MOSFET". [5]

#### Unit-II'

- (a) Derive  $I_{ds} V_{ds}$  relationship for MOSFET. Also prove that the drain current  $I_D = C(1 + \lambda V_{DS})$ in case of channel length modulation. Where C =  $\frac{1}{2}K'_{n}\left(\frac{W}{L}\right)(V_{GS}-V_{t})^{2}, \lambda = \text{process technology}$ parameter.

- The NMOS device with  $V_t = 0.7V$  has its source terminal grounded and a 1.3v is applied to gate. The device has  $\mu_n$ ,  $C_{ox} = 100 \ \mu A/V^2$ ,  $W = 10 \ \mu m$ , L =1  $\mu$ m. Find the value of drain current for  $V_D = 3V.[4]$

### OR

- Prove that the pull-up to pull-down ratio for a (a)NMOS inverter is 4:1 when it is driven by another [8] inverter.

- Derive the  $\beta_n/\beta_p$  ratio of a CMOS Inverter. [8](b)

### (Unit-'III')

- Implement clocked S-R Flip-Flop using CMOS (a) [8]Inverter.

- [5] Explain transistor sizing of CMOS. (b)

- [3] Implement OR gate using transmission gate. (c)

- Realize the following logic expression using CMOS (a) Inverter:

- $A.B + \overline{A}.\overline{B}$ (*i*)

- A.B.C + A.B.C(ii)

- (iii) A.B.C.D

- (iv) AB + BC + AC

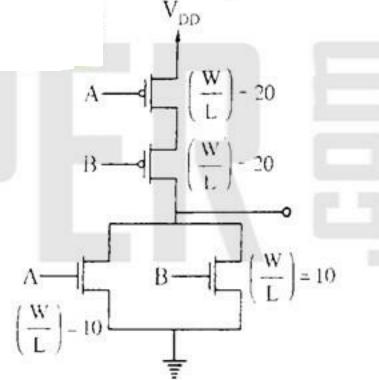

(b) Find the equivalent (W/L) ratio of NMOS and PMOS transistors in the given CMOS circuit. [6]

#### Unit-TV'

- (a) Draw the stick diagrams of

- (i) 3 i/p NAND gate

- (ii) 3 i/p NOR gate

- [4+4=8]

- (b) Write a short note on "Layout optimization for performance". [8]

#### OR

- 4. (a) Draw the stick diagram and layout for the following boolean expression Y = A.B + C.D + E

- (b) What is "Euler path"? What is use of it? Explain with a suitable example. [8]

#### (Unit-V)

- 5. What do you meant by VHDL? (a) Write a VHDL code for

- Full Adder (i)

- J-K Flip-flop

- [2+4+4=10]

- Distinguish between

- Signal and variable (i)

- [3] Concurrent and sequential Assignment. [3]

- Write a VHDL code for: (a)

- S-R Flip-Flop.

- 4 bits adder using full adder.

- Explain: (b)

- Entity declaration

- [2]

[8]

- Behavioral style of modelling tural style of modelling

- [3] [3]